采用了分层和电路块的模块设计

Design Gateway可以将希望标准化的功能块或模块作为标准电路块进行库化,标准电路块在沿用该模块的电路中可以像元器件库那样进行搜索和输入。

另外,电路块在沿用目的地中可设定各种编辑权限,沿用设计时可使用与应用相对应的电路块。

沿用源电路块更新时,可以按元器件、NET等对象提取与沿用目的地电路块的差异。

另外,在沿用目的地电路块中反映沿用源电路块的信息时,由于能够按差异保持沿用目的地的信息,因此也能应对希望使沿用目的地电路块的编辑内容优先的情况。

Design Gateway是支持包括单个PCB板、或多个PCB板与PCB板之间的连接在内的整个系统电路的设计/验证的电路设计环境,在世界上尚无先例。能够以多个PCB板为对象进行分析和设计变更,开放性高,可与IT通信基础设施密切协作。

另外,支持对自上向下/自下向上设计进行辅助的分层功能、使用了标准电路块的沿用设计、以及在电气模块化设计中的运用等,预期可大幅削减工时,提高质量。

Design Gateway可以将希望标准化的功能块或模块作为标准电路块进行库化,标准电路块在沿用该模块的电路中可以像元器件库那样进行搜索和输入。

另外,电路块在沿用目的地中可设定各种编辑权限,沿用设计时可使用与应用相对应的电路块。

沿用源电路块更新时,可以按元器件、NET等对象提取与沿用目的地电路块的差异。

另外,在沿用目的地电路块中反映沿用源电路块的信息时,由于能够按差异保持沿用目的地的信息,因此也能应对希望使沿用目的地电路块的编辑内容优先的情况。

Design Gateway可以根据元器件或NET中设定的属性,进行各种规则校验。由于不使用仿真器,因此只需最低限度的必要信息即可进行实用性很高的校验。

通过在NET中设定电压值,可以实施纳入了元器件的电气特性(常数、额定值)的元器件可靠性校验,立即发现疏忽大意导致的设计错误,比如元器件反向连接、元器件选择错误导致的额定值不足等。

除了考虑了电气特性的校验以外,还可以进行参照的重复、NET名称的重复和接触、电源/地线的短路以及属性的遗漏等校验,并以错误报告书的形式显示结果。错误报告书可以与电路图进行交叉搜索,迅速确认错误部位。

Design Gateway可以在电路设计初期阶段轻松地进行SI分析。分析工具具备下列特点,任何人都能轻松使用。

● 模型设定简便易行(无模型、自动分配)

● 直观半自动化的简便操作面板

● 以对比图等适合分析的形式输出结果

● 追求结果的重复使用性(重新显示、加工、文档化)

在设计中途也可以立即分析关键NET,因此消除了在电路完成之后将所有NET都输出到仿真系统之类的繁琐性。

Design Gateway支持Windows的标准API“COM”,开放性高,可与电路设计时需要的基础设施环境中积累的技术信息无缝协作。

不但可以与Engineering PLM DS-2无缝协作,而且还可以与原有系统协同作业,构建用户特有的设计环境。根据不同协作方式,备有合适的界面。

实现了“DS-CR Embedded for Design Gateway”,可以在Design Gateway上使用DS-CR功能直接访问DS-CR管理的元器件信息及设计信息。由此,可以进一步强化电路设计环境。

・ 元器件主信息的使用

・ PCB板元器件列表的创建及管理

・ 设计数据的管理及使用

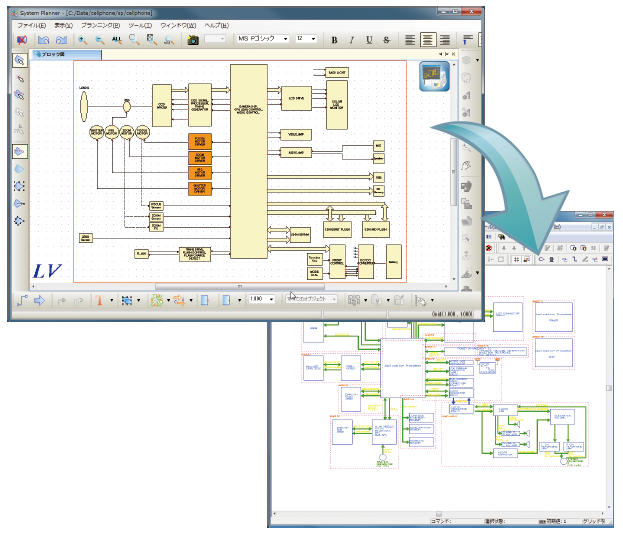

构思设计环境“System Planner”中创建的系统图,可以直接作为Design Gateway的系统电路读入。

另外,可以从系统电路创建对应于多个PCB板的网表信息,利用系统级多板设计环境Design Force,在连接了多个PCB板的状态下进行多板布局设计。

支持使用了FPGA/CPLD、嵌入设备专用微处理器的设计,实现了与设备供应商的密切协作。

可与PCB-FPGA协同设计辅助工具“GPM”协同作业,支持设备供应商提供的FPGA开发工具、设计工具包。

另外,为了支持难度日益加大的电子设备设计,通过与第三方供应商的设计工具实现密切协作,来强有力地支持整个电路设计/验证环境。